IDF 2009: Threaded DDR3 Memory Modules

Rambus & Kingston Develop Threaded Module Prototype

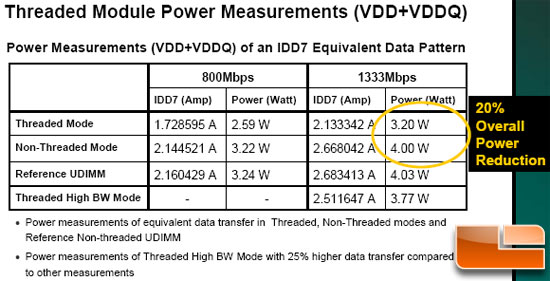

Rambus and Kingston recently announced that they have successfully co-developed a threaded DDR3 memory module or improved multi-core computing. What makes this announcement interesting is that the initial test results have shown an improvement in data throughput of up to 50 percent, while reducing power consumption by 20 percent compared to conventional DDR3 memory modules. Since more and more consumers are becoming environmentally conscious and worried about their Carbon footprint this discovery might help conserve power, increase battery life, and actually improve performance numbers for throughput-intensive computing tasks.

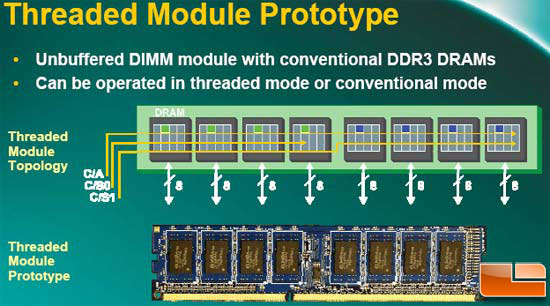

Threaded memory module technology is implemented utilizing industry-standard DDR3 devices and a conventional module infrastructure. It is capable of providing greater power efficiency for computing systems by partitioning modules into multiple independent channels that share a common command/address port. Threaded modules can support 64-byte memory transfers at full bus utilization, resulting in efficiency gains of up to 50 percent when compared to current DDR3 memory modules. In addition, DRAMs in threaded modules are activated half as often as in conventional modules, resulting in a 20 percent reduction in overall module power. The only issue with this threaded module is that it can’t be used in any of the DDR3 motherboards on the market today since updates are needed to the board itself.

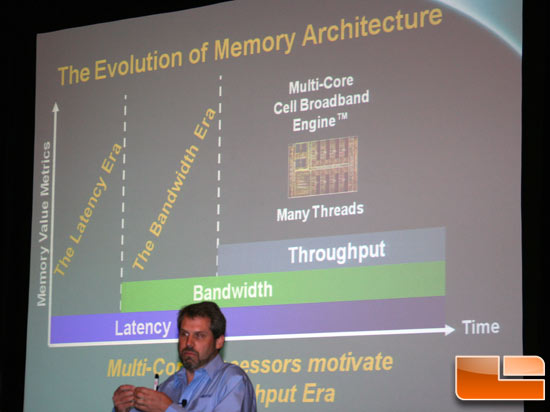

Legit Reviews got a chance to attend a workshop given by Craig Hampel, Rambus Fellow. He gave an in-depth background on memory architecture and how threaded memory is the ideal direction to go.

To show how the module is able to reduce power consumption by 20 percent compared to conventional DDR3 memory modules the following slide was presented by Kingston Technology. It looks like threaded modules are an interesting concept as partitioning modules into multiple independent channels that share a common command/address port really does make sense with the multi-core processors on the market today. We had to leave the briefing threaded memory a little early for another meeting, but we’ll bring you more coverage on threaded memory when we get a chance to talk to Rambus privately later today.

Comments are closed.